- 您现在的位置:买卖IC网 > Sheet目录1203 > COREPCIF-RM (Microsemi SoC)IP MODULE COREPCIF

�� �

�

�

�CorePCIF� Parameters�

�CorePCIF� is� a� highly� configurable� core.� The� configuration� is� controlled� by� approximately� 50� top-level� parameters.�

�These� are� listed� in� Table� 4-1� to� Table� 4-4� on� page� 39� .�

�General� Configuration� Parameters�

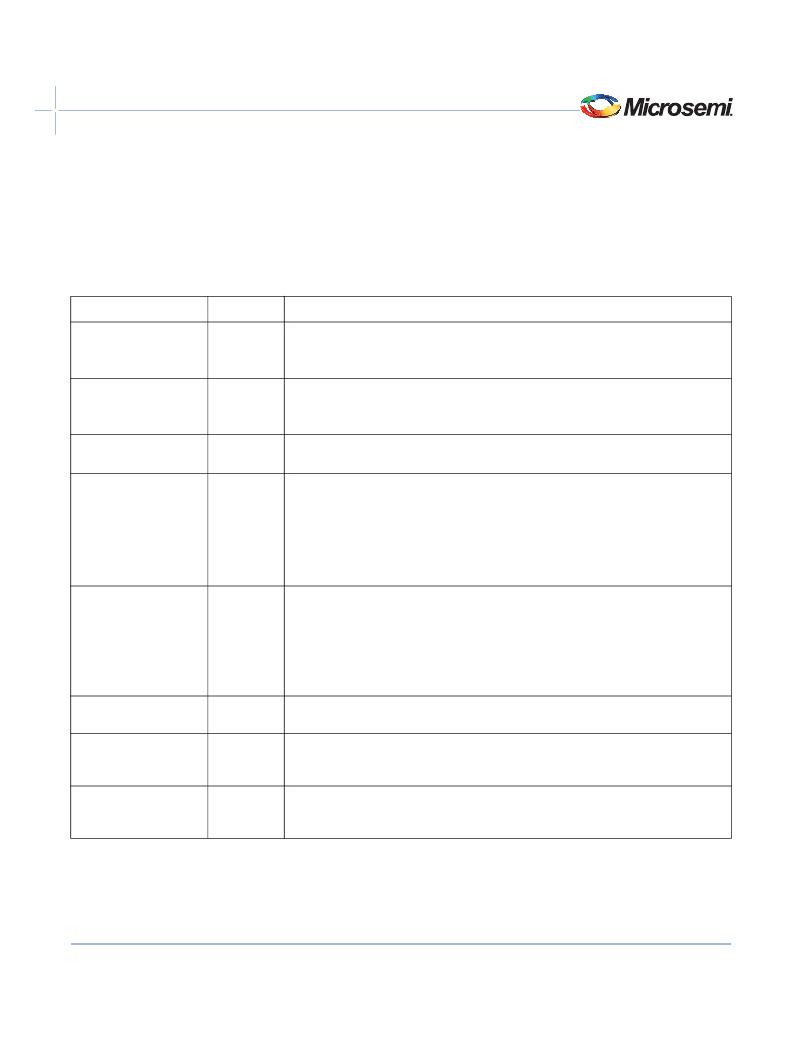

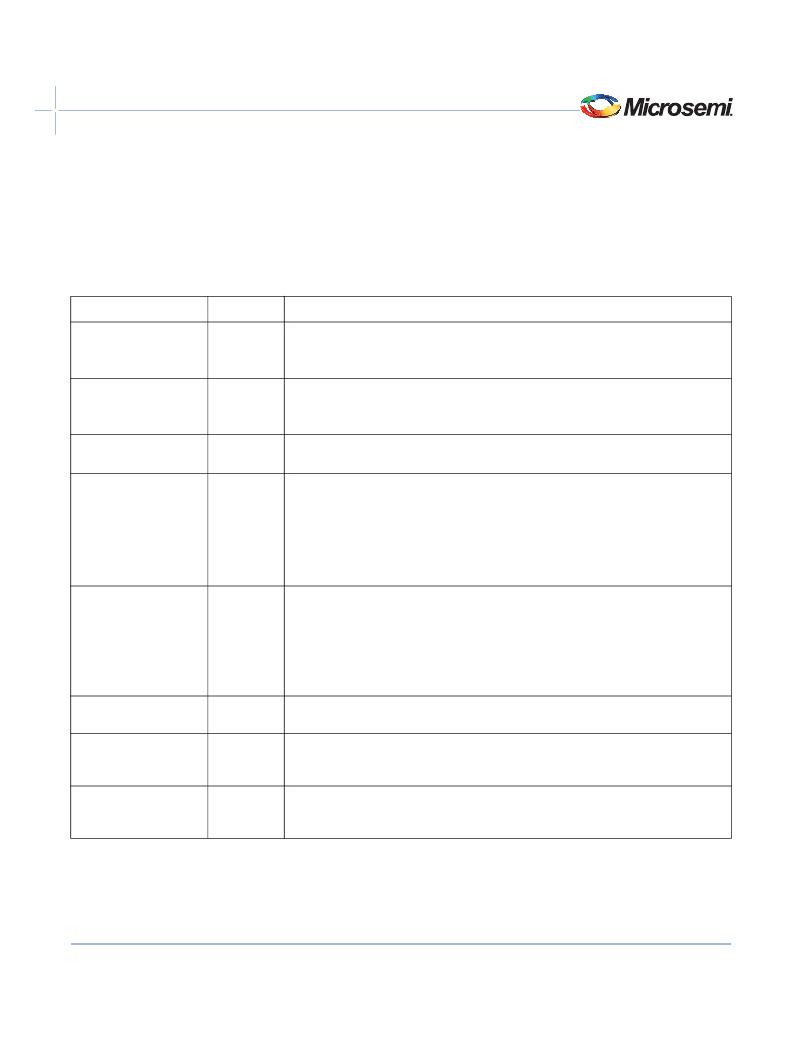

��Table� 4-1� ·� General� Parameters�

�4�

�Name�

�FAMILY�

�MASTER�

�TARGET�

�PCI_FREQ�

�SLOW_READ�

�PCI_WIDTH�

�DISABLE_WDOG�

�DISABLE_BAROV�

�REMOVE_CAP_ID�

�Values�

�8� to� 21�

�0� or� 1�

�0� or� 1�

�33� or� 66�

�0� or� 1�

�32� or� 64�

�0� or� 1�

�0� or� 1�

�0� or� 1�

�Description�

�Must� be� set� to� the� required� FPGA� family:�

�8:� SX-A�

�9:� RTSX-S�

�11:� Axcelerator�

�12:� RTAX-S�

�14:� ProASIC� PLUS�

�15:� ProASIC3�

�16:� ProASIC3E�

�17:� Fusion�

�20:� IGLOO�

�21:� IGLOOe�

�22:� ProASIC3L�

�When� 1,� the� PCI� Master� function� with� DMA� controller� is� implemented.�

�When� 1,� the� PCI� Target� function� is� implemented.�

�When� 66,� the� 66� MHz� bit� in� the� PCI� configuration� space� is� set.�

�When� 1,� the� core� inserts� either� one� or� two� wait� states� in� all� read� transfers,� eliminating� the�

�requirement� for� internal� data� storage� within� the� core.� This� parameter� must� not� be� set� if� the�

�FIFO� recovery� option� is� enabled.�

�Sets� 32-� or� 64-bit� PCI� implementation.�

�When� 1,� the� data� transfer� watchdog� inside� the� core� is� disabled.� The� core� normally� includes� a�

�transfer� watchdog� that� will� terminate� a� PCI� cycle� if� the� backend� logic� fails� to� provide� or� accept�

�data� within� the� time� limits� defined� by� the� PCI� specification.� This� function� can� be� disabled� in�

�embedded� systems� if� longer� access� times� are� permitted.�

�When� 1,� the� core� will� not� disconnect� when� a� memory� or� I/O� transfer� overflows� the� BAR� as�

�required� by� the� PCI� specification.� Instead,� the� core� will� wrap� the� address� and� jump� to� the�

�beginning� of� the� BAR� space.� Setting� the� parameter� to� 1� will� reduce� the� number� of� logic�

�elements� in� the� core.� When� the� BAR� overflow� logic� is� enabled,� the� core� may� disconnect� burst�

�transfers� before� they� reach� the� upper� limit� of� the� BAR,� depending� on� the� transfer� rate�

�controlled� by� IRDY� and� TRDY.� This� may� require� the� PCI� Master� to� perform� several� separate�

�PCI� transfers� before� the� top� of� memory� is� reached.�

�When� 1,� the� capability� pointer� and� capability� values� in� the� PCI� configuration� space� are� all� held�

�at� 0.� The� interrupt� and� DMA� control� registers� are� still� accessible� at� locations� 48� and� 50–5C� hex.�

�When� 0,� the� capability� IDs� are� as� described� in� Table� 7-1� on� page� 105� and� Table� 7-2� on�

��v4.0�

�35�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

COREU1LL-AR

IP MODULE COREU1LL

COREU1PHY-AR

IP MODULE COREU1PHY

CORR-8BIT-XM-UT2

SITE LICENSE IP CORRELATOR XP

CP2-GSA-L

CONN SHIELD LOWER TYPE A 22

CP2-HSA110-1

CONN SHROUD CPCI 2MM TYPE A 22

CP2-HSC055-4

CONN SHROUD CPCI 2MM TYPE C 11

CP2-K3567-SR-F

COMPACT PCI - MISC

CP2105EK

KIT EVAL FOR CP2105

相关代理商/技术参数

COREPCIF-RMFL

功能描述:IP MODULE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1

COREPCIF-UR

功能描述:HW/SW/OTHER 制造商:microsemi corporation 系列:* 零件状态:在售 标准包装:1

COREPCI-SN

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-SR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-UR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-XX

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPRO LEDBULB 10.5-60W B

制造商:Philips Lumileds 功能描述:

COREPRO LEDBULB 10.5-60W E

制造商:Philips Lumileds 功能描述: